## **DUV Photolithography**

There are significant differences between typical UV photolithography and DUV photolithography. Due to the shorter wavelengths used there is much higher absorption of energy in the standard novolak resist polymers, necessitating the use of very different polymer chemistries such as polyhydroxystyrene (PHS), acrylic polymer, and phenolic resin. More significant is that all DUV resists are **Chemically Amplified** and require that a **Post-Exposure Bake** be performed to achieve the expected results. The PEB time and temperature are critical to the final resist dimensions and must be carefully controlled. For this and other reasons **Automated** resist coating, baking, and development are strongly recommended.

The increased reflectivity of silicon and most other materials at DUV wavelengths also presents problems. To control the reflected energy from the surface most DUV processes use an **Anti-Reflective Coating** layer, usually applied to the wafer first. These layers can be conformal or planarizing, and while typically removed through dry etching can also be developable. One important advantage of using ARC is that most resist adhesion issues are minimized. Use of ARC for DUV exposures whenever possible is recommended.

Another important difference is the reduced **Depth of Focus** available from DUV projection tools. Due to the use of shorter wavelengths and larger lenses the DOF is often less than the desired thickness of photoresist. Many strategies are used to overcome this, including hard masks and bilayer resist schemes. Most DUV tools also allow **Numerical Aperture** adjustment and various illumination choices to compensate. The reduced DOF also requires that all wafer and reticle surfaces be extremely clean to prevent any tilt or bow which would severely affect results.

One problematic difference is found in inspection of results. Because of the small dimensions produced, much of the inspection must be done using **Scanning Electron Microscopes**. This process is time-consuming and expensive, but may be the only effective method available for accurate determination of results. Note that SEM inspection of uncoated DUV photoresist causes resist shrinkage, affecting measurements.

## **Process Considerations**

## **WARNING:**

<u>DO NOT</u> use any materials other than supplied DUV photoresist without specific permission from the tool owners. Contamination of the lens is **NOT REVERSABLE** and results in **PERMENANT DAMAGE**. The lens is a million dollar instrument and has already been degraded by unknown material usage.

DUV processing allows very little substrate non-flatness due to the very limited depth of focus. Your substrates should ideally be **Ultra-Flat Wafers** (TTV <2um). If not, there may be focus variations within single die. Note that CNF does not sell Ultra-flat wafers at this time. Any contamination on the back of the wafer will result in either poor exposure results or wafer handler failure, and can contaminate the wafer chuck for all users. Wafers stuck in the tool due to back side contamination can sometimes be removed using the **Mat Hdl - Remove Wafers** operation. If this should fail they will have to be removed by Staff, delaying your work. <u>Inspect the backs of your wafers every time</u>.

Reticles must be very clean, with <u>NO PHOTORESIST</u> on the chrome. <u>Any</u> contamination will cause your and other users' results to suffer. Contamination of the reticle **Platen** requires careful cleaning by Staff and will delay your work. If there is <u>any</u> visible contamination on your reticle you need to clean it before use.

Use caution removing, carrying, and replacing the reticle SMIF boxes. The bottom can and has fallen out from them. ALWAYS keep one hand under the box. Treat the interior of the box as an especially clean space.

Wafers should be coated with photoresist as closely as possible to the exposure time. Chemically amplified resists do not age well and your results can change significantly if long delays before exposure are introduced. Similarly, wafers should be baked and developed as soon as possible after exposure to prevent degradation due to airborne contamination. It is recommended that wafers be processed within one hour after exposure. Changes in delay times may result in changes to results.

Focus and dose characterization is required for all processes. The DOF in DUV is very limited and best focus can be affected by many factors including feature geometry. Determination of best focus must be done in combination with dose testing as each can influence the other.

As in all photolithographic processing consistency is critical to reproducibility of results. Film thicknesses, bake times and temperatures, and develop processes all need to be carefully controlled, and become increasingly important as features shrink in size. Time and effort spent in characterization will ensure reproducible results and save troubleshooting later. Staff is available for consultation regarding all aspects of processing.

Alignment of process layers is typically very good, but is affected by the quality of your marks. Please refer to the following section regarding best practices.

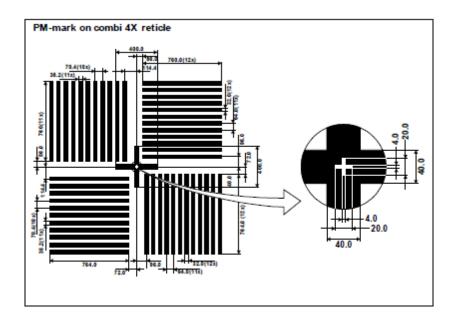

## **ASML PM Mark**

The alignment system used on the **ASML** stepper is somewhat different than that on the GCA tools. One interesting difference is that the user does not need to include wafer marks in their pattern design. The ASML can print the <u>PM Marks</u> at locations specified by the user. The advantages are both that the user has less to consider during design, and that the mark locations can be selected independently of any pattern or wafer layout parameters. The etched depth of the PM marks is important and should be as close to <u>120nm deep</u> as possible (or odd multiples of 120) as the system uses a phase-contrast detection system. Note that some transparent layer marks may cause issues; consult the Photolith staff.

The alignment marks are typically printed in a Zero layer so that the etch depth can be well controlled. Marks should not be printed in a device layer unless the process for that layer is known to yield good marks. Marks can be placed individually or automatically distributed by the software. Scribe lane alignment marks are also available. Back-side PM marks can only be located at  $\pm 26.8$ mm and  $\pm 30.6$ mm and need to target a  $\underline{160}$ nm depth. All alignments are performed automatically without user intervention unless errors halt the process.